## **TMC2250A**

# Matrix Multiplier 12 x 10 bit, 50 MHz

### **Features**

- Four user-selectable filtering and transformation functions:

- Triple dot product (3 x 3) matrix multiply

- Cascadeable 9-tap systolic FIR filter

- Cascadeable 3 x 3-pixel image convolver

- Cascadeable 4 x 2-pixel image convolver

- 50 MHz (20ns) pipelined throughput

- 12-bit input and output data, 10-bit coefficients

- 6-bit cascade input and output ports in all filter modes

- Onboard coefficient storage, with three-cycle updating of all nine coefficients

## **Applications**

- Image filtering and manipulation

- Video effects generation

- Video standards conversion and encoding/decoding

- Three-dimensional image manipulation

- Medical image processing

- Edge detection for object recognition

- FIR filtering for communications systems

## **Description**

The TMC2250A is a flexible high-performance nine-multiplier array VLSI circuit which can execute a cascadeable 9-tap FIR filter, a cascadeable 4 x 2 or 3 x 3-pixel image convolution, or a 3 x 3 color space conversion. All configurations offer throughput at up to the maximum guaranteed 50 MHz clock rate with 12-bit data and 10-bit coefficients. All inputs and outputs are registered on the rising edges of the clock.

The 3 x 3 matrix multiply or color conversion configuration can perform video standard conversion (YIQ or YUV to RGB, etc.) or three-dimensional perspective translation at real-time video rates.

The 9-tap FIR filter configuration, useful in Video, Telecommunications, and Signal Processing, features a 16-bit cascade input to allow construction of longer filters.

The cascadeable 3 x 3 and 4 x 2-pixel image convolver functions allow the user to perform numerous image processing functions, including static filters and edge detectors. The 16-bit cascade input port facilitates two-chip 50 MHz cubic convolution (4 x 4-pixel kernel).

The TMC2250A is fabricated in a sub-micron CMOS process and operates at clock speeds of up to 50 MHz over the full commercial (0°C to 70°C) temperature and supply voltage ranges. It is available in 121-pin plastic pin grid array (PGA) packages as well as a 120-lead plastic quad flatpack (PQFP). All input and output signals are TTL compatible.

## **Functional Description**

The TMC2250A is a nine-multiplier array with the internal bus structure and summing adders needed to implement a 3 x 3 matrix multiplier (triple dot product) a cascadeable 9-tap FIR filter, a 3 x 3-pixel convolver, or a 4 x 2-pixel convolver all in one monolithic circuit. With a 50MHz guaranteed maximum clock rate, this device offers video and imaging system designers a single-chip solution to numerous common image and signal-processing problems.

The three data input ports (A, B, C) accept 12-bit two's complement integer data, which is also the format for the output ports (X, Y, Z) in the matrix multiply mode (Mode 00). In the filter configurations (Modes 01, 10, and 11) the cascade ports assume 12-bit integer, 4-bit fractional two's complement data on both input and output. The coefficient input ports (KA, KB, KC) are always 10-bit two's complement fractional. Table 1 details the bit weighting of the input and output data in all configurations.

### **Operating Modes**

The TMC2250A can implement four different digital filter architectures. Upon selection of the desired function by the user (MODE1-0), the device reconfigures its internal data paths and input and output buses appropriately. The output ports (XC, YC and ZC) are configured in all filter modes a 16-bit Cascade In and Cascade Out ports so that multiple devices can be connected to build larger filters. These modes are described individually below. The I/O function configurations for all four modes are shown in Table 1.

### **Definitions**

The calculations performed by the TMC2250A in each mode are also shown below, utilizing the following notation:

### A(1), B(5), C(2), CASIN(3)

Indicates the data word presented to that input port during the specified clock rising edge(x). Applies to all input ports  $A_{11-0}$ ,  $B_{11-0}$ ,  $C_{11-0}$ , and  $CASIN_{15-0}$ .

### KA1(1), KB3(4)

Indicates coefficient data stored in the specified one of the nine onboard coefficient registers KA1 through KC3, as shown in the block diagram for that mode, input during or before the specified clock rising edge (x).

### X(1), Y(4), Z(6), CASOUT (6)

Indicated data available at that output port t<sub>DO</sub> after that specified clock rising edge (x). Applies to all output ports X<sub>11</sub>-0, Y<sub>11</sub>-0, Z<sub>11</sub>-0, and CASOUT<sub>15</sub>-0.

### **Numeric Format**

Table 2 shows the binary weightings of the input and output ports of the TMC2250A. Although the internal sums of products could grow to 23 bits, in the matrix multiply mode (Mode 00) the outputs X, Y and Z are rounded to yield 12-bit integer words. Thus the output format is identical to the input data format. In the filter configurations (Modes 01, 10, and 11) the cascade output is always half-LSB rounded to 16 bits, specifically 12 integer bits and 4 fractional guard bits, with no overflow "headroom". The user is of course free to half-LSB round the output word to any size less than 16 bits by forcing a 1 into the bit position of the cascade input immediately below the desired LSB. In all modes, bit weighting is easily adjusted if desired by applying the same scaling correction factor to both input and output data words. If the coefficients are rescaled, the relative weightings of the CASIN and CASOUT ports will differ accordingly.

### **Data Overflow**

As shown in Table 2, the TMC2250A's matched input and output data formats accommodate 0dB (unity) gain. Therefore, the user must be aware of input conditions that could lead to numeric overflow. Maximum input data and coefficient word sizes must be taken into account with the specific algorithm performed to ensure that no overflow occurs.

**Table 1. Data Port Formatting by Mode**

|      |       | Inputs            |                   |       |                   |       |                       | Output               |      | Outputs               |                        |  |

|------|-------|-------------------|-------------------|-------|-------------------|-------|-----------------------|----------------------|------|-----------------------|------------------------|--|

| Mode | A11-0 | B11-0             | C11-0             | KA9-0 | KB9-0             | KC9-0 | XC11-0                | YC11-8               | Y7-4 | YC3-0                 | ZC <sub>11-0</sub>     |  |

| 00   | A11-0 | B <sub>11-0</sub> | C <sub>11-0</sub> | KA9-0 | KB <sub>9-0</sub> | KC9-0 | X11-0                 | Y <sub>11-8</sub>    | Y7-4 | Y <sub>3-0</sub>      | Z <sub>11-0</sub>      |  |

| 01   | A11-0 | B <sub>11-0</sub> | NC                | KA9-0 | KB <sub>9-0</sub> | KC9-0 | CASIN <sub>15-4</sub> | CASIN <sub>3-0</sub> | NC   | CASOUT <sub>3-0</sub> | CASOUT <sub>15-4</sub> |  |

| 10   | A11-0 | B11-0             | C11-0             | KA9-0 | KB9-0             | KC9-0 | CASIN <sub>15-4</sub> | CASIN <sub>3-0</sub> | NC   | CASOUT <sub>3-0</sub> | CASOUT <sub>15-4</sub> |  |

| 11   | A11-0 | B <sub>11-0</sub> | NC                | KA9-0 | KB <sub>9-0</sub> | KC9-0 | CASIN <sub>15-4</sub> | CASIN <sub>3-0</sub> | NC   | CASOUT <sub>3-0</sub> | CASOUT <sub>15-4</sub> |  |

Table 2. Bit Weightings for Input and Output Data Words

| Bit Weights                   | 2 <sup>11</sup> | 2 <sup>10</sup>  | 2 <sup>9</sup>   | 2 <sup>8</sup>   | 2 <sup>7</sup>   | 2 <sup>6</sup>   | 2 <sup>5</sup> | 2 <sup>4</sup>  | 2 <sup>3</sup> | 2 <sup>2</sup> | 2 <sup>1</sup>  | 2 <sup>0</sup>  |   | 2-1 | 2-2             | 2-3             | 2-4             | 2 <sup>-5</sup> | 2 <sup>-6</sup> | 2-7            | 2 <sup>-8</sup> | 2-9            |

|-------------------------------|-----------------|------------------|------------------|------------------|------------------|------------------|----------------|-----------------|----------------|----------------|-----------------|-----------------|---|-----|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|-----------------|----------------|

| Inputs                        |                 |                  |                  |                  |                  |                  |                |                 |                |                |                 |                 |   |     |                 |                 |                 |                 |                 |                |                 |                |

| All Modes<br>Data A, B, C     | -l11            | l <sub>10</sub>  | 19               | 18               | 17               | 16               | <b>I</b> 5     | 14              | 13             | 12             | l <sub>1</sub>  | lo              |   |     |                 |                 |                 |                 |                 |                |                 |                |

| Coefficients<br>KA, KB, KC    |                 |                  |                  |                  |                  |                  |                |                 |                |                |                 | -K9             |   | K8  | K7              | K <sub>6</sub>  | K <sub>5</sub>  | K4              | K3              | K <sub>2</sub> | K <sub>1</sub>  | K <sub>0</sub> |

| Modes 01, 10,<br>11<br>CASIN  | -CI15           | CI <sub>14</sub> | CI <sub>13</sub> | CI <sub>12</sub> | CI11             | CI <sub>10</sub> | CI9            | CI8             | CI7            | CI6            | CI <sub>5</sub> | CI4             |   | CI3 | CI <sub>2</sub> | CI1             | CI <sub>0</sub> |                 |                 |                |                 |                |

| Internal Sum                  | X20             | X19              | X18              | X17              | X16              | X15              | X14            | X13             | X12            | X11            | X10             | Х9              |   | Х8  | X7              | Х6              | X5              | X4              | Х3              | X2             | X1              | X <sub>0</sub> |

| Outputs                       |                 |                  |                  |                  |                  |                  |                |                 |                |                |                 |                 |   |     |                 |                 |                 |                 |                 |                |                 |                |

| Mode 00<br>X, Y, Z            | -011            | 010              | 09               | 08               | 07               | 06               | 05             | 04              | 03             | 02             | 01              | 00              |   |     |                 |                 |                 |                 |                 |                |                 |                |

| Modes 01, 10,<br>11<br>CASOUT | -CO15           | CO14             | CO13             | CO <sub>12</sub> | CO <sub>11</sub> | CO <sub>10</sub> | CO9            | CO <sub>8</sub> | CO7            | CO6            | CO <sub>5</sub> | CO <sub>4</sub> | • | CO3 | CO <sub>2</sub> | CO <sub>1</sub> | CO <sub>0</sub> |                 |                 |                |                 |                |

Note: A minus sign indicates a two's complement sign bit.

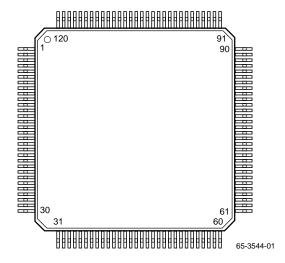

## **Pin Assignments**

## 120 Pin Plastic Quad Flat Pack (MQFP), KE Package

| Pin | Name             | Pin | Name             | Pin | Name             | Pin | Name              |

|-----|------------------|-----|------------------|-----|------------------|-----|-------------------|

| 1   | XC <sub>6</sub>  | 31  | ZC <sub>6</sub>  | 61  | KA <sub>1</sub>  | 91  | B <sub>5</sub>    |

| 2   | XC5              | 32  | ZC7              | 62  | KA <sub>2</sub>  | 92  | B6                |

| 3   | XC4              | 33  | ZC <sub>8</sub>  | 63  | KA3              | 93  | В7                |

| 4   | XC <sub>3</sub>  | 34  | GND              | 64  | KA <sub>4</sub>  | 94  | B8                |

| 5   | XC <sub>2</sub>  | 35  | ZC <sub>9</sub>  | 65  | KA <sub>5</sub>  | 95  | В9                |

| 6   | XC <sub>1</sub>  | 36  | ZC <sub>10</sub> | 66  | KA <sub>6</sub>  | 96  | B <sub>10</sub>   |

| 7   | XC <sub>0</sub>  | 37  | ZC <sub>11</sub> | 67  | KA7              | 97  | B11               |

| 8   | GND              | 38  | KC <sub>0</sub>  | 68  | KA <sub>8</sub>  | 98  | C <sub>0</sub>    |

| 9   | YC11             | 39  | KC <sub>1</sub>  | 69  | KA9              | 99  | C <sub>1</sub>    |

| 10  | YC <sub>10</sub> | 40  | KC <sub>2</sub>  | 70  | CWE <sub>1</sub> | 100 | C <sub>2</sub>    |

| 11  | YC <sub>9</sub>  | 41  | KC <sub>3</sub>  | 71  | CWE <sub>0</sub> | 101 | C <sub>3</sub>    |

| 12  | VDD              | 42  | GND              | 72  | GND              | 102 | VDD               |

| 13  | YC <sub>8</sub>  | 43  | KC <sub>4</sub>  | 73  | A <sub>0</sub>   | 103 | C <sub>4</sub>    |

| 14  | Y7               | 44  | KC5              | 74  | A1               | 104 | C <sub>5</sub>    |

| 15  | Y <sub>6</sub>   | 45  | KC <sub>6</sub>  | 75  | A <sub>2</sub>   | 105 | C <sub>6</sub>    |

| 16  | GND              | 46  | VDD              | 76  | Аз               | 106 | GND               |

| 17  | Y5               | 47  | KC7              | 77  | A4               | 107 | C <sub>7</sub>    |

| 18  | Y4               | 48  | KC <sub>8</sub>  | 78  | A5               | 108 | C <sub>8</sub>    |

| 19  | YC <sub>0</sub>  | 49  | KC <sub>9</sub>  | 79  | A <sub>6</sub>   | 109 | C <sub>9</sub>    |

| 20  | VDD              | 50  | KB <sub>0</sub>  | 80  | A <sub>7</sub>   | 110 | C <sub>10</sub>   |

| 21  | YC1              | 51  | KB <sub>1</sub>  | 81  | A8               | 111 | C11               |

| 22  | YC2              | 52  | KB <sub>2</sub>  | 82  | A9               | 112 | MODE <sub>1</sub> |

| 23  | YC3              | 53  | KB3              | 83  | A10              | 113 | MODE <sub>0</sub> |

| 24  | GND              | 54  | KB4              | 84  | A11              | 114 | GND               |

| 25  | ZC <sub>0</sub>  | 55  | KB <sub>5</sub>  | 85  | B <sub>0</sub>   | 115 | XC11              |

| 26  | ZC <sub>1</sub>  | 56  | KB <sub>6</sub>  | 86  | B <sub>1</sub>   | 116 | XC <sub>10</sub>  |

| 27  | ZC <sub>2</sub>  | 57  | KB <sub>7</sub>  | 87  | B <sub>2</sub>   | 117 | XC <sub>9</sub>   |

| 28  | ZC <sub>3</sub>  | 58  | KB <sub>8</sub>  | 88  | CLK              | 118 | VDD               |

| 29  | ZC4              | 59  | KB9              | 89  | В3               | 119 | XC <sub>8</sub>   |

| 30  | ZC <sub>5</sub>  | 60  | KA <sub>0</sub>  | 90  | B4               | 120 | XC <sub>7</sub>   |

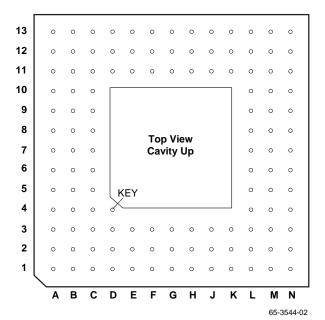

## Pin Assignments (continued)

## 120 Pin Plastic Grid Array, H5 Package

| Pin | Name              | Pin | Name             | Pin | Name             | Pin | Name             |

|-----|-------------------|-----|------------------|-----|------------------|-----|------------------|

| A1  | XC <sub>7</sub>   | C5  | GND              | G11 | А3               | L10 | KB <sub>8</sub>  |

| A2  | XC <sub>9</sub>   | C6  | C <sub>10</sub>  | G12 | A <sub>2</sub>   | L11 | KA <sub>1</sub>  |

| A3  | XC <sub>10</sub>  | C7  | GND              | G13 | А3               | L12 | KA <sub>5</sub>  |

| A4  | MODE <sub>0</sub> | C8  | VDD              | H1  | Y4               | L13 | KA <sub>6</sub>  |

| A5  | C <sub>11</sub>   | C9  | C <sub>0</sub>   | H2  | YC <sub>0</sub>  | M1  | ZC <sub>2</sub>  |

| A6  | C <sub>8</sub>    | C10 | B <sub>8</sub>   | НЗ  | VDD              | M2  | ZC <sub>7</sub>  |

| A7  | C <sub>7</sub>    | C11 | B <sub>5</sub>   | H11 | GND              | МЗ  | ZC <sub>9</sub>  |

| A8  | C <sub>5</sub>    | C12 | В3               | H12 | A <sub>0</sub>   | M4  | ZC <sub>11</sub> |

| A9  | C <sub>3</sub>    | C13 | B <sub>1</sub>   | H13 | A1               | M5  | KC <sub>2</sub>  |

| A10 | C <sub>1</sub>    | D1  | YC <sub>11</sub> | J1  | YC <sub>1</sub>  | M6  | KC4              |

| A11 | B <sub>10</sub>   | D2  | XC <sub>0</sub>  | J2  | YC <sub>2</sub>  | M7  | KC <sub>6</sub>  |

| A12 | В7                | D3  | XC <sub>0</sub>  | J3  | GND              | M8  | KC9              |

| A13 | В4                | D11 | CLK              | J11 | KA8              | M9  | KB <sub>2</sub>  |

| B1  | XC <sub>4</sub>   | D12 | B <sub>0</sub>   | J12 | CWE <sub>1</sub> | M10 | KB <sub>5</sub>  |

| B2  | XC <sub>5</sub>   | D13 | A <sub>10</sub>  | J13 | CWE <sub>0</sub> | M11 | KB <sub>9</sub>  |

| В3  | XC <sub>8</sub>   | E1  | YC <sub>9</sub>  | K1  | YC <sub>3</sub>  | M12 | KA <sub>2</sub>  |

| B4  | XC <sub>11</sub>  | E2  | YC <sub>10</sub> | K2  | ZC <sub>0</sub>  | M13 | КАз              |

| B5  | MODE <sub>1</sub> | E3  | GND              | K3  | ZC3              | N1  | ZC <sub>5</sub>  |

| B6  | C <sub>9</sub>    | E11 | A11              | K11 | KA4              | N2  | ZC8              |

| B7  | C <sub>6</sub>    | E12 | A9               | K12 | KA7              | N3  | ZC <sub>10</sub> |

| B8  | C <sub>4</sub>    | E13 | A8               | K13 | KA9              | N4  | KC <sub>1</sub>  |

| B9  | C <sub>2</sub>    | F1  | Y7               | L1  | ZC <sub>1</sub>  | N5  | KC <sub>3</sub>  |

| B10 | B <sub>11</sub>   | F2  | YC <sub>8</sub>  | L2  | ZC <sub>4</sub>  | N6  | KC <sub>5</sub>  |

| B11 | В9                | F3  | VDD              | L3  | ZC <sub>6</sub>  | N7  | KC7              |

| B12 | В6                | F11 | A7               | L4  | GND              | N8  | KC <sub>8</sub>  |

| B13 | В2                | F12 | A <sub>6</sub>   | L5  | KC <sub>0</sub>  | N9  | KB <sub>1</sub>  |

| C1  | XC <sub>1</sub>   | F13 | A5               | L6  | GND              | N10 | KB3              |

| C2  | XC <sub>2</sub>   | G1  | Y5               | L7  | VDD              | N11 | KB <sub>6</sub>  |

| C3  | XC <sub>6</sub>   | G2  | Y <sub>6</sub>   | L8  | KB <sub>0</sub>  | N12 | KB <sub>7</sub>  |

| C4  | $V_{DD}$          | G3  | GND              | L9  | KB <sub>4</sub>  | N13 | KA <sub>0</sub>  |

## **Pin Descriptions**

|                    | Pin N                                                                     | umber                                                                   |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name           | PGA                                                                       | MQFP                                                                    | Function                    | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Power              |                                                                           |                                                                         |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VDD                | F3, H3, L7,<br>C8, C4                                                     | 12, 20, 46,<br>102, 118                                                 | Supply<br>Voltage           | The TMC2250A operates from a single +5V supply. All pins must be connected.                                                                                                                                                                                                                                                                                                                                                                       |

| GND                | E3, G3, J3,<br>L4, L6, H11,<br>C7, C5                                     | 8, 16, 24, 34,<br>42, 72, 106,<br>114                                   | Ground                      | The TMC2250A operates from a single +5V supply. All pins must be connected.                                                                                                                                                                                                                                                                                                                                                                       |

| Clock              |                                                                           |                                                                         |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CLK                | D11                                                                       | 88                                                                      | System<br>Clock             | The TMC2250A operates from a single system clock input. All timing specifications are referenced to the rising edge of clock.                                                                                                                                                                                                                                                                                                                     |

| Controls           |                                                                           |                                                                         |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MODE1,0            | B4, A4                                                                    | 112, 113                                                                | Mode Control                | The TMC2250A will switch to the configuration selected by the user (as shown in Table 3) on the next clock. This registered control is usually static; however, should the user wish to switch between modes, the internal pipeline latencies of the device must be taken into account. Valid data will not be available at the outputs in the new configuration until enough clocks in the new mode have passed to flush the internal registers. |

| CWE <sub>1,0</sub> | J12, J13                                                                  | 70, 71                                                                  | Coefficient<br>Write Enable | Data presented to the coefficient input ports (KA, KB, and KC) will update three of the internal coefficient storage registers, as indicated by the simultaneous Coefficient Write Enable select, on the next clock. See Table 4 and the Functional Block Diagram.                                                                                                                                                                                |

| Input/Outp         | ut                                                                        | •                                                                       |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| A11-0              | E11, D13,<br>E12, E13,<br>F11, F12,<br>F13, G13,<br>G11, G12,<br>H13, H12 | 84, 83, 82, 81,<br>80, 79, 78, 77,<br>76, 75, 74, 73                    | Data Input A                | Data presented to the 12-bit registered data input ports A, B, and C are latched into the multiplier input registers for the currently selected configuration (Table 3). In all modes except Mode 00, new data are internally right-shifted to the next filter tap on each rising edge of CLK.                                                                                                                                                    |

| B <sub>11</sub> -0 | B10, A11,<br>B11, C10,<br>A12, B12,<br>C11, A13,<br>C12, B13,<br>C13, D12 | 97, 96, 95, 94,<br>93, 92, 91, 90,<br>89, 87, 86, 85                    | Data Input B                |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| C <sub>11</sub> -0 | A5, C6, B6,<br>A6, A7, B7,<br>A8, B8, A9,<br>B9, A10, C9                  | 111, 110,<br>109, 108,<br>107, 105,<br>104, 103,<br>101, 100, 99,<br>98 | Data Input C                |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

## Pin Descriptions (continued)

|                   | Pin Number                                                   |                                                       |                                                           |                                                                                                                                                                                                                                                                   |

|-------------------|--------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name          | PGA                                                          | MQFP                                                  | Function                                                  | Pin Description                                                                                                                                                                                                                                                   |

| KA9-0             | K13, J11,<br>K12, L13,<br>L12, K11,<br>M13, M12,<br>L11, N13 | 69, 68, 67, 66,<br>65, 64, 63, 62,<br>61, 60          | Coefficient<br>Input A1, A2,<br>A3                        | Data presented to the 10-bit registered coefficient input ports KA, KB and KC are latched three at a time into the internal coefficient storage register set indicated by the Coefficient Write Enable CWE <sub>1,0</sub> on the next clock, as shown in Table 4. |

| KB9-0             | M11, L10,<br>N12, N11,<br>M10, L9,<br>N10, M9, N9,<br>L8     | 59, 58, 57, 56,<br>55, 54, 53, 52,<br>51, 50          | Coefficient<br>Input B1, B2,<br>B3                        |                                                                                                                                                                                                                                                                   |

| KC9-0             | M8, N8, N7,<br>M7, N6, M6,<br>N5, M5, N4,<br>L5              | 49, 48, 47, 45,<br>44, 43, 41, 40,<br>39, 38          | Coefficient<br>Input B1, B2,<br>B3                        |                                                                                                                                                                                                                                                                   |

| XC11-0            | B4, A3, A2,<br>B3, A1, C3,<br>B2, B1, D3,<br>C2, C1, D2      | 115, 116,<br>117, 119,<br>120, 1, 2, 3, 4,<br>5, 6, 7 | CASIN <sub>15-4</sub> /<br>Output X                       | In all modes except Mode 00, the x port and four bits of the Y output port are reconfigured as the 16-bit registered Cascade Input port CASIN <sub>15-0</sub> . Data presented to this input will be added to the weighted                                        |

| YC11-8            | D1, E2, E1,<br>F2                                            | 9, 10, 11, 13                                         | CASIN <sub>3-0</sub> /<br>Output Y <sub>11-0</sub>        | sums of the data words which were presented to the input ports (A, B and C).                                                                                                                                                                                      |

| Y7-4              | F1, G2, G1,<br>H1                                            | 14, 15, 17, 18                                        | Output <sub>7-4</sub><br>only                             | In the matrix multiply mode, data are available at the 12-bit registered output ports X, Y AND Z tDO after                                                                                                                                                        |

| YC <sub>3-0</sub> | K1, J2, J1,<br>H2                                            | 23, 22, 21, 19                                        | CASOUT <sub>3-0</sub> /<br>Output Y <sub>3-0</sub>        | every clock. These ports are reconfigured in the filtering modes as 16-bit Cascade Input and Output ports.CASOUT <sub>15-0</sub>                                                                                                                                  |

| ZC11-0            | M4, N3, M3,<br>N2, M2, L3,<br>N1, L2, K3,<br>M1, L1, K2      | 37, 36, 35, 33,<br>32, 31, 30, 29,<br>28, 27, 26, 25  | CASOUT <sub>15</sub> -<br>4/Output Z <sub>11</sub> -<br>0 | In all modes except Mode 00, the Z port and four bits of the Y output port are reconfigured as the 16-bit registered Cascade Output port CASOUT <sub>15-0</sub> .                                                                                                 |

- 1. The output ports X, Y, Z and CASOUT, and input port CASIN are internally reconfigured by the device as required for each mode of the device. The multiple-function pins have names which are combinations of these titles, as appropriate.

- 2. The output drivers on pins XC<sub>11-0</sub> and YC<sub>11-8</sub> are not necessarily disabled until after the first rising edge of CLK following power-up. If these pins are to be tied to other output drivers, to each other, or to ground or V<sub>DD</sub>, the user should ensure that a clock pulse arrives within a few seconds of power-up, to avoid bus contention.

**Table 3. Configuration Mode Word**

| MODE <sub>1,0</sub> | Configuration Mode        |

|---------------------|---------------------------|

| 00                  | 3 x 3 Matrix Multiply     |

| 01                  | 9-Tap One Dimensional FIR |

| 10                  | 3 x 3 -Pixel Convolver    |

| 11                  | 4 x 2 -Pixel Convolver    |

**Table 5. Coefficient Input Ports**

| Input Port | Registers Available |

|------------|---------------------|

| KA         | KA1, KA2, KA3       |

| KB         | KB1, KB2, KB3       |

| KC         | KC1, KC2, KC3       |

**Table 4. Coefficient Write Enable Word**

| CWE <sub>1,0</sub> | Coefficient Set Selected |

|--------------------|--------------------------|

| 00                 | Hold all registers       |

| 01                 | Update KA1, KB1, KC1     |

| 10                 | Update KA2, KB2, KC2     |

| 11                 | Update KA3, KB3, KC3     |

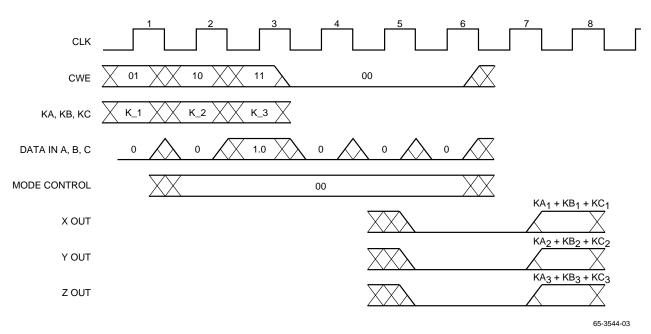

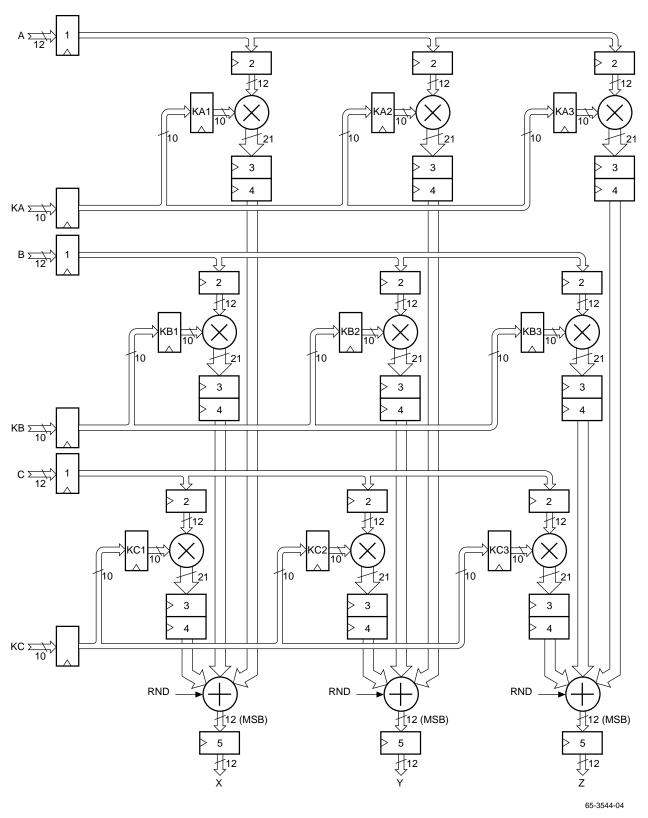

## 3 x 3 Matrix Multiplier (Mode 00)

This mode utilizes all six input and output ports in the basic configuration to realize a "triple dot product", in which each output is the sum of all three input words in that column multiplied by the appropriate stored coefficients. The three corresponding sums of products are available at the outputs five clock cycles after the input data are latched, and three new

data words half-LSB rounded to 12 bits are then available every clock cycle.

X(5)=A(1)KA1(1)+B(1)KB1(1)+C(1)KC1(1) Y(5)=A(1)KA2(1)+B(1)KB2(1)+C(1)KC2(1) Z(5)=A(1)KA3(1)+B(1)KB3(1)+C(1)KC3(1)

Figure 1. 3 x 3 Matrix Multiplier Impulse Response (Mode 00)

Figure 2. 3 x 3 Matrix Multiplier Configuration (Mode 00)

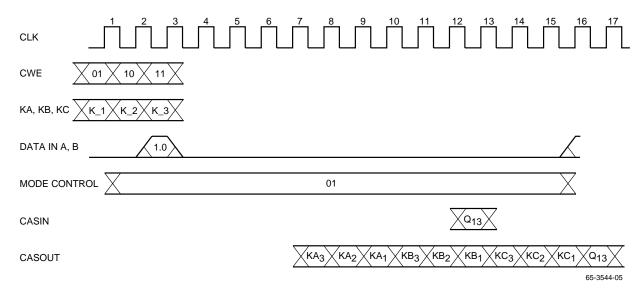

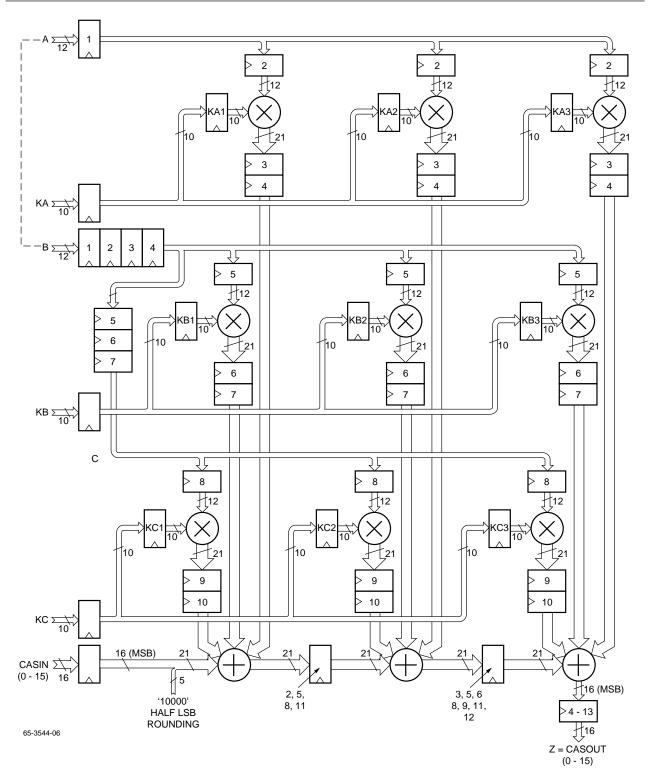

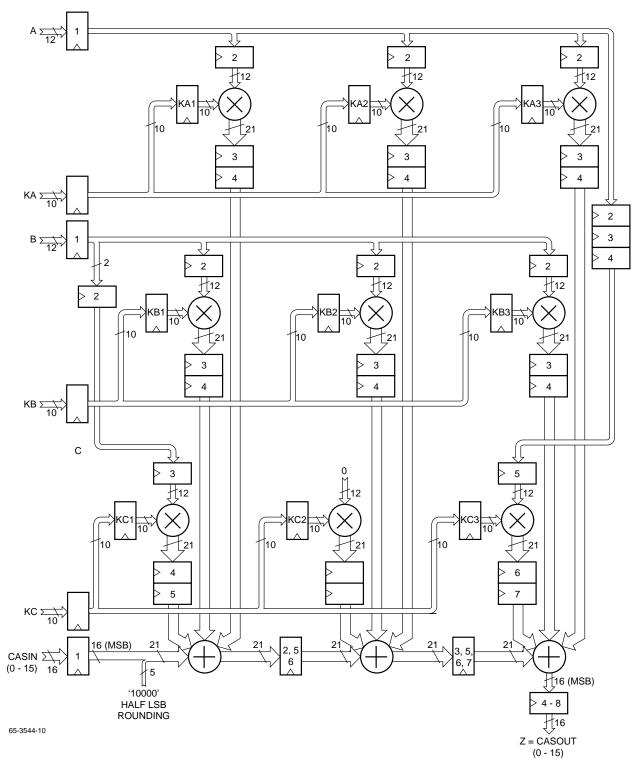

## 9-Tap FIR Filter Mode (01)

The architecture for this configuration is shown in Figure 4. The user loads the desired coefficient set, presents input data to ports A and B simultaneously (most applications will wire the A and B inputs together), and receives the resulting 9-sample response, half-LSB rounded to 16 bits, 5 to 13 clock cycles later. A new output data word is available every clock cycle.

The figure shows that the input data are automatically right-shifted by one position through the row of multiplier input registers on every clock in anticipation of a new input data word.

CASOUT(13) =

A(9)KA3(9)+A(8)KA2(8)+A(7)KA1(7)

+B(6)KB3(9)+B(5)KB2(8)+B(4)KB1(7)

+B(3)KC3(9)+B(2)KC2(8)+B(1)KC1(7)

+CASIN(10)

Latency: Impulse in to center of 9-tap response =9 registers. Cascade In to Cascade Out=4 registers.

Figure 3. 9-Tap FIR Filter Impulse Response (Mode 01)

Figure 4. 9-Tap FIR Filter Configuration (Mode 01)

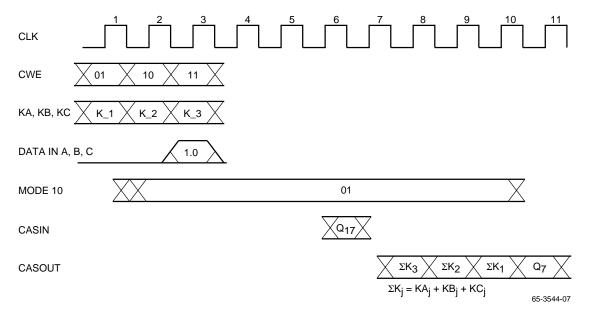

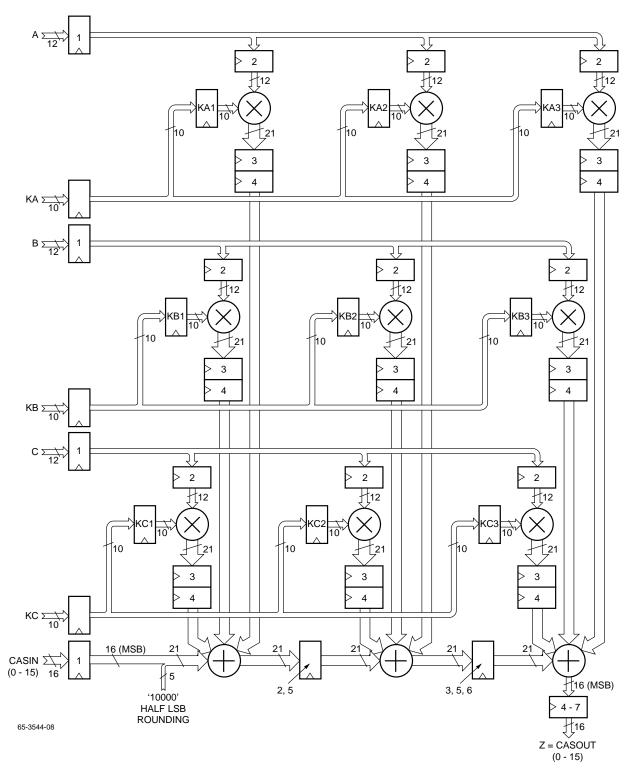

## 3 x 3 Pixel Convolver (Mode 10)

This filter configuration accepts a 3 pixel-square neighborhood, side-loaded three pixels at a time through input ports A, B and C, and multiplies the 9 most recent pixel values by the coefficient set currently stored in the registers. These products are summed with the data presented to the cascade input, and a new 3-cycle impulse response, rounded to 16 bits, is available at the output port 5 to 7 clocks later, with a new output available on every clock cycle.

The input pixel data are automatically shifted one location to the right through the three rows of multiplier input registers on every clock in anticipation of three new input data words, effectively sliding the convolutional window over one column in an image plane.

### CASOUT(7)=

A(3)KA3(3)+A(2)KA2(2)+A(1)KA1(1)

+B(3)KB3(3)+B(2)KB2(2)+B(1)KB1(1)

+C(3)KC3(3)+C(2)KC2(2)+C(1)KC1(1)

+CASIN(4)

Latency: Impulse in to center of 3-tap response = 6 registers. Cascade In to Cascade Out=4 registers.

Figure 5. 3 x 3-Pixel Convolver Impulse Response (Mode 10)

Figure 6. 3 x 3-Pixel Convolver Configuration (Mode 10)

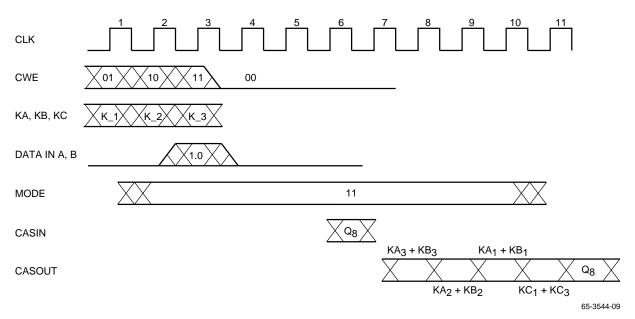

## 4 x 2-Pixel Cascadeable Convolver (Mode 11)

Similar to Mode 10, the 4 x 2 -Pixel convolver allows the use to perform full-speed cubic convolution with only two TMC2250A devices and the TMC2111A Pipeline Delay Register to synchronize the cascade ports (see the Applications Discussion section).

Pixel data are side-loaded into ports A and B, multiplied by the onboard coefficients, summed with the cascade input, and half-LSB rounded to 16 bits. The four-cycle impulse response emerges at the cascade output port 5 to 8 clock cycles later. A new output word is available on every clock cycle. Note that Multiplier KC2 is not used in this mode and that its stored coefficient is ignored.

As shown below, the column of input pixel data is automatically shifted one location to the right through the two rows of multiplier input registers on every clock in anticipation of two new input data words, effectively sliding the convolutional window over one column in an image plane.

### CASOUT(8)=

A(4)KA3(4)+A(3)KA2(3)+A(2)KA1(2) +A(1)KB3(4)+B(4)KB3(4)+B(3)KB2(3) +B(2)KB1(2)+B(1)KC1(2)+CASIN(5)

Figure 7. 4 x 2-Pixel Convolver Impulse Response (Mode 11)

Figure 8. 4 x 2-Pixel Convolver Configuration (Mode 11)

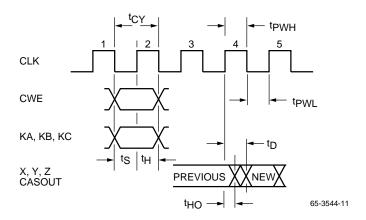

Figure 9. Input/Output Timing Diagram

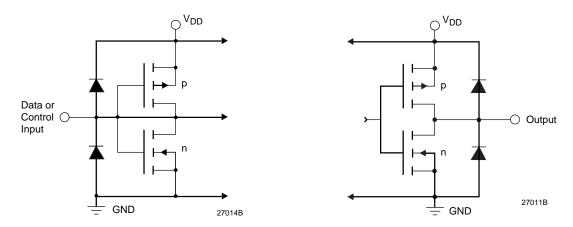

Figure 10. Equivalent Digital Input Circuit Figure 11. Equivalent Digital Output Circuit

## **Absolute Maximum Ratings**

(beyond which the device may be damaged)<sup>1</sup>

| Parameter                                                      | Min  | Тур | Max                   | Unit |

|----------------------------------------------------------------|------|-----|-----------------------|------|

| Supply Voltage                                                 | -0.5 |     | 7.0                   | V    |

| Input Voltage                                                  | -0.5 |     | V <sub>DD</sub> + 0.5 | V    |

| Applied Voltage <sup>2</sup>                                   | -0.5 |     | V <sub>DD</sub> + 0.5 | V    |

| Externally Forced Current <sup>3,4</sup>                       | -3.0 |     | 6.0                   | mA   |

| Short Circuit Duration (single output in HIGH state to ground) |      |     | 1                     | sec  |

| Operating, Ambient Temperature                                 | -20  |     | 110                   | °C   |

| Junction Temperature                                           |      |     | 140                   | °C   |

| Storage Temperature                                            | -65  |     | 150                   | °C   |

| Lead Soldering Temperature (10 seconds)                        |      |     | 300                   | °C   |

### Notes:

- 1. Functional operation under any of these conditions is NOT implied. Performance and reliability are guaranteed only if Operating Conditions are not exceeded.

- 2. Applied voltage must be current limited to specified range.

- 3. Forcing voltage must be limited to specified range.

- 4. Current is specified as conventional current flowing into the device.

## **Operating Conditions**

| Param | eter                           |            | Min  | Nom | Max  | Units |

|-------|--------------------------------|------------|------|-----|------|-------|

| VDD   | Power Supply Voltage           |            | 4.75 | 5.0 | 5.25 | V     |

| fCLK  | Clock Frequency                | TMC2250A   |      |     | 30   | MHz   |

|       |                                | TMC2250A-2 |      |     | 40   | MHz   |

|       |                                | TMC2250A-3 |      |     | 50   | MHz   |

| tPWH  | CLK pulse width, HIGH          |            | 6    |     |      | ns    |

| tpwL  | CLK pulse width, LOW           |            | 8    |     |      | ns    |

| ts    | Input Data Setup Time          |            | 6    |     |      | ns    |

| tH    | Input Data Hold Time           |            | 2    |     |      | ns    |

| ViH   | Input Voltage, Logic HIGH      |            | 2.0  |     |      | V     |

| VIL   | Input Voltage, Logic LOW       |            |      |     | 0.8  | V     |

| Іон   | Output Current, Logic HIGH     |            |      |     | -2.0 | mA    |

| loL   | Output Current, Logic LOW      |            |      |     | 4.0  | mA    |

| TA    | Ambient Temperature, Still Air |            | 0    |     | 70   | °C    |

## **Electrical Characteristics**

| Param | neter                                                    | Conditions                                                              | Min | Тур | Max | Units |

|-------|----------------------------------------------------------|-------------------------------------------------------------------------|-----|-----|-----|-------|

| IDD   | Total Power Supply                                       | V <sub>DD</sub> = Max, C <sub>LOAD</sub> = 25pF, f <sub>CLK</sub> = Max |     |     |     |       |

|       | Current                                                  | TMC2250A                                                                |     |     | 125 | mA    |

|       |                                                          | TMC2250A-2                                                              |     |     | 140 | mA    |

|       |                                                          | TMC2250A-3                                                              |     |     | 155 | mA    |

| IDDU  | Power Supply Current,                                    | V <sub>DD</sub> = Max, <del>OE</del> = HIGH, f <sub>CLK</sub> =Max      |     |     |     |       |

|       | Unloaded                                                 | TMC2250A                                                                |     |     | 120 | mA    |

|       |                                                          | TMC2250A-2                                                              |     |     | 135 | mA    |

|       |                                                          | TMC2250A-3                                                              |     |     | 150 | mA    |

| IDDQ  | Power Supply Current,<br>Quiescent                       | V <sub>DD</sub> = Max, CLK = LOW                                        |     |     | 12  | mA    |

| CPIN  | I/O Pin Capacitance                                      |                                                                         |     | 5   |     | pF    |

| lін   | Input Current, HIGH <sup>1</sup>                         | V <sub>DD</sub> = Max, V <sub>IN</sub> = V <sub>DD</sub>                |     |     | ±5  | μΑ    |

| IJЦ   | Input Current, LOW1                                      | V <sub>DD</sub> = Max, V <sub>IN</sub> = 0 V                            |     |     | ±5  | μΑ    |

| lozh  | Hi-Z Output Leakage<br>Current, Output HIGH <sup>2</sup> | V <sub>DD</sub> = Max, V <sub>IN</sub> = V <sub>DD</sub>                |     |     | ±10 | μΑ    |

| lozL  | Hi-Z Output Leakage<br>Current, Output LOW <sup>2</sup>  | V <sub>DD</sub> = Max, V <sub>IN</sub> = 0 V                            |     |     | ±10 | μΑ    |

| los   | Short-Circuit Current                                    |                                                                         | -20 |     | -80 | mA    |

| Voн   | Output Voltage, HIGH                                     | IOH = Max, VDD = Min                                                    | 2.4 |     |     | V     |

| Vol   | Output Voltage, LOW                                      | I <sub>OL</sub> = Max, V <sub>DD</sub> = Min                            |     |     | 0.4 | V     |

### Notes:

- 1. Except pins XC<sub>11-0</sub>, YC<sub>11-8</sub>.

- 2. Pins XC11-0, YC11-8.

## **Switching Characteristics**

| Parameter |                   | Conditions    | Min | Тур | Max | Units |

|-----------|-------------------|---------------|-----|-----|-----|-------|

| tDO       | Output Delay Time | CLOAD = 25 pF |     |     | 15  | ns    |

| tHO       | Output Hold Time  | CLOAD = 25 pF | 3   |     |     | ns    |

## **Application Notes**

### **Performing Large-Kernel Pixel Interpolation**

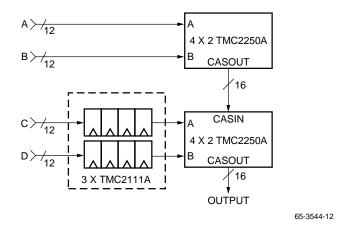

The Cascade Input and Output Ports of the TMC2250A allow the user to stack multiple devices to perform larger interpolation kernels with no decrease in pixel throughput. Figure 12 illustrates a basic application utilizing Mode 11 to realize a 4 x 4-pixel kernel, also called Cubic Convolution.

This example utilizes the TMC2011A Variable-Length Shift Register to compensate for the internal latency of each TMC2250A. Alternatively, some applications may utilize RAM, FIFO's, or other methods to store multiple-line pixel data. In these cases the user may compensate for latency by simply offsetting the access sequencing of the storage devices.

Figure 12. Performing Cubic Convolution with Two TMC2250A's

### **Related Products**

- TMC2301 Image Resampling Sequencer

- TMC2302 Image Manipulation Sequencer

- TMC2249A Video Mixer

- TMC2242B Half-Band Filter

## **Mechanical Dimensions**

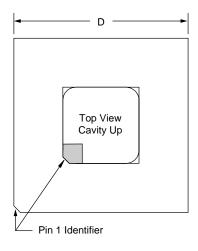

## 121-Lead PPGA Package

| Cumbal | Inches    |       | Millin    | Notes |       |

|--------|-----------|-------|-----------|-------|-------|

| Symbol | Min.      | Max.  | Min.      | Max.  | Notes |

| Α      | .080      | .160  | 2.03      | 4.06  |       |

| A1     | .040      | .060  | 1.01      | 1.53  |       |

| A2     | .125      | .215  | 3.17      | 5.46  |       |

| øΒ     | .016      | .020  | 0.40      | 0.51  | 2     |

| øB2    | .050 NOM. |       | 1.27 NOM. |       | 2     |

| D      | 1.340     | 1.380 | 33.27     | 35.05 | SQ    |

| D1     | 1.200 BSC |       | 30.48 BSC |       |       |

| е      | .100 BSC  |       | 2.54      |       |       |

| L      | .110      | .145  | 2.79      | 3.68  |       |

| L1     | .170      | .190  | 4.31      | 4.83  |       |

| М      | 13        |       | 13        |       | 3     |

| N      | 120       |       | 12        | 4     |       |

| Р      | .003 —    |       | .076      | _     |       |

- 1. Pin #1 identifier shall be within shaded area shown.

- 2. Pin diameter excludes solder dip finish.

- 3. Dimension "M" defines matrix size.

- 4. Dimension "N" defines the maximum possible number of pins.

- 5. Orientation pin is at supplier's option.

- 6. Controlling dimension: inch.

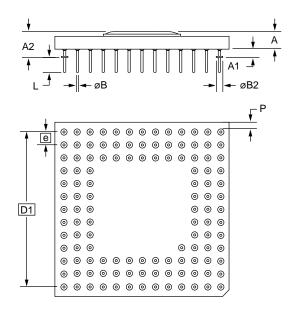

## **Mechanical Dimensions** (continued)

### 120-Lead MQFP Package

Α1

| Cumbal | Inches    |       | Millim  | Notes |       |  |

|--------|-----------|-------|---------|-------|-------|--|

| Symbol | Min.      | Max.  | Min.    | Max.  | Notes |  |

| Α      | _         | .154  | _       | 3.92  |       |  |

| A1     | .010      | _     | .25     | _     |       |  |

| A2     | .125      | .144  | 3.17    | 3.67  |       |  |

| В      | .012      | .018  | .30     | .45   | 3, 5  |  |

| С      | .005      | .009  | .13     | .23   | 5     |  |

| D/E    | 1.219     | 1.238 | 30.95   | 31.45 |       |  |

| D1/E1  | 1.098     | 1.106 | 27.90   | 28.10 |       |  |

| е      | .0315 BSC |       | .80 BSC |       |       |  |

| L      | .026      | .037  | .65     | .95   | 4     |  |

| N      | 120       |       | 120     |       |       |  |

| ND     | 30        |       | 30      |       |       |  |

| α      | 0°        | 7°    | 0°      | 7°    |       |  |

| CCC    | _         | .004  | _       | .10   |       |  |

- 1. All dimensions and tolerances conform to ANSI Y14.5M-1982.

- 2. Controlling dimension is millimeters.

- 3. Dimension "B" does not include dambar protrusion. Allowable dambar protrusion shall be .08mm (.003in.) maximum in excess of the "B" dimension. Dambar cannot be located on the lower

13/.30 .005/.012 R

- 4. "L" is the length of terminal for soldering to a substrate.

- 5. "B" & "C" includes lead finish thickness.

LEAD COPLANARITY

△ ccc C

## **Ordering Information**

| Product Number | Temperature<br>Range | Speed<br>Grade | Screening  | Package                        | Package<br>Marking |

|----------------|----------------------|----------------|------------|--------------------------------|--------------------|

| TMC2250AH5C    | 0°C to 70°C          | 30 MHz         | Commercial | 120 Pin Plastic Pin Grid Array | 2250AH5C           |

| TMC2250AH5C2   | 0°C to 70°C          | 40 MHz         | Commercial | 120 Pin Plastic Pin Grid Array | 2250AH5C2          |

| TMC2250AH5C3   | 0°C to 70°C          | 50 MHz         | Commercial | 120 Pin Plastic Pin Grid Array | 2250AH5C3          |

| TMC2250AKEC    | 0°C to 70°C          | 30 MHz         | Commercial | 120 Lead Plastic Quad Flatpack | 2250AKEC           |

| TMC2250AKEC2   | 0°C to 70°C          | 40 MHz         | Commercial | 120 Lead Plastic Quad Flatpack | 2250AKEC2          |

| TMC2250AKEC3   | 0°C to 70°C          | 50 MHz         | Commercial | 120 Lead Plastic Quad Flatpack | 2250AKEC3          |

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com